- 全部

- 默认排序

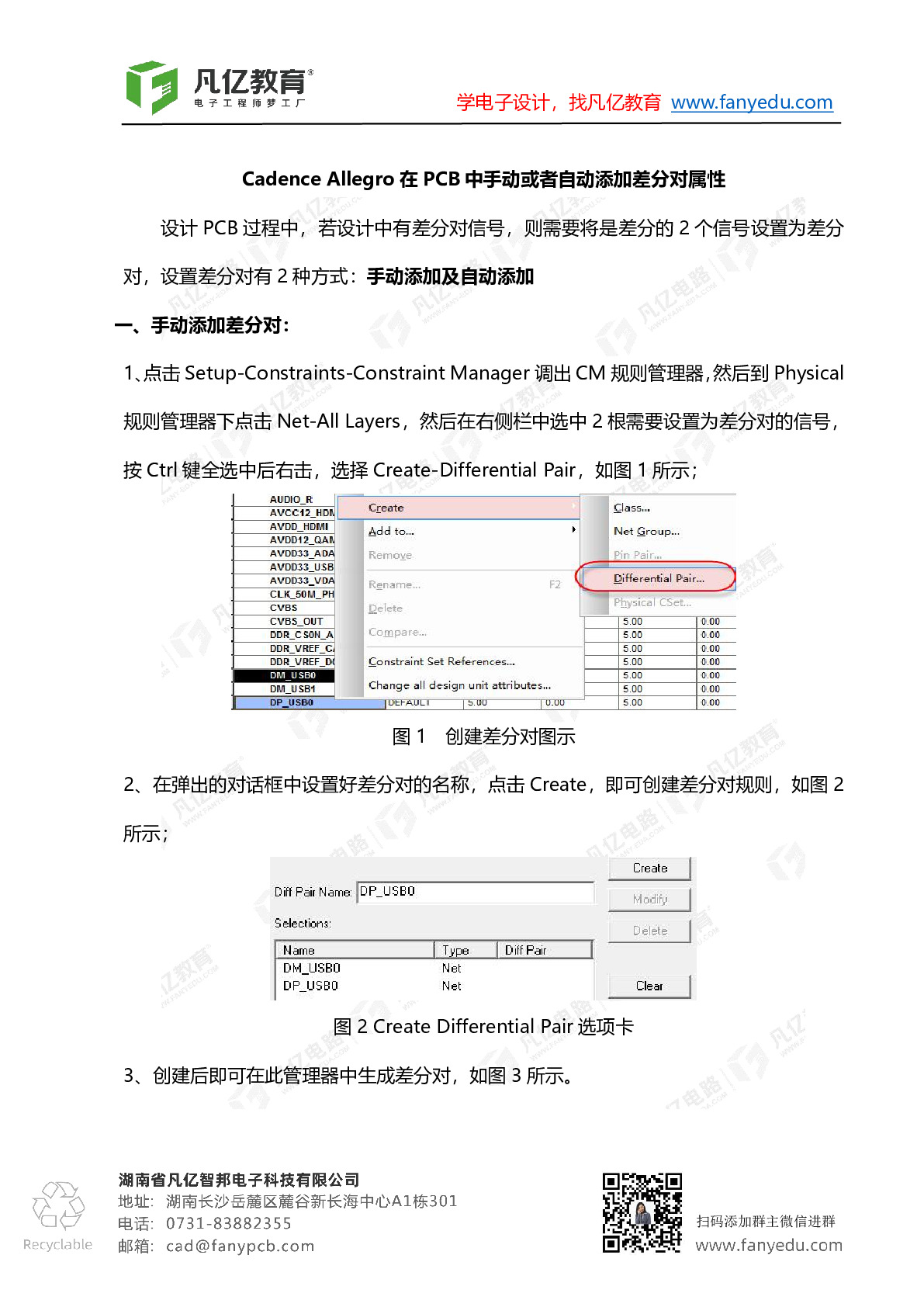

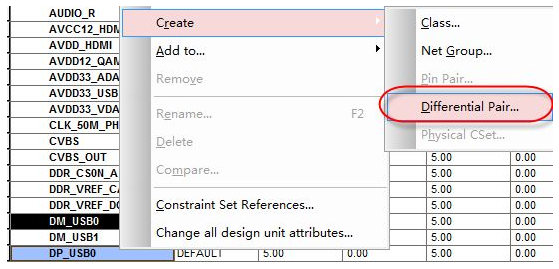

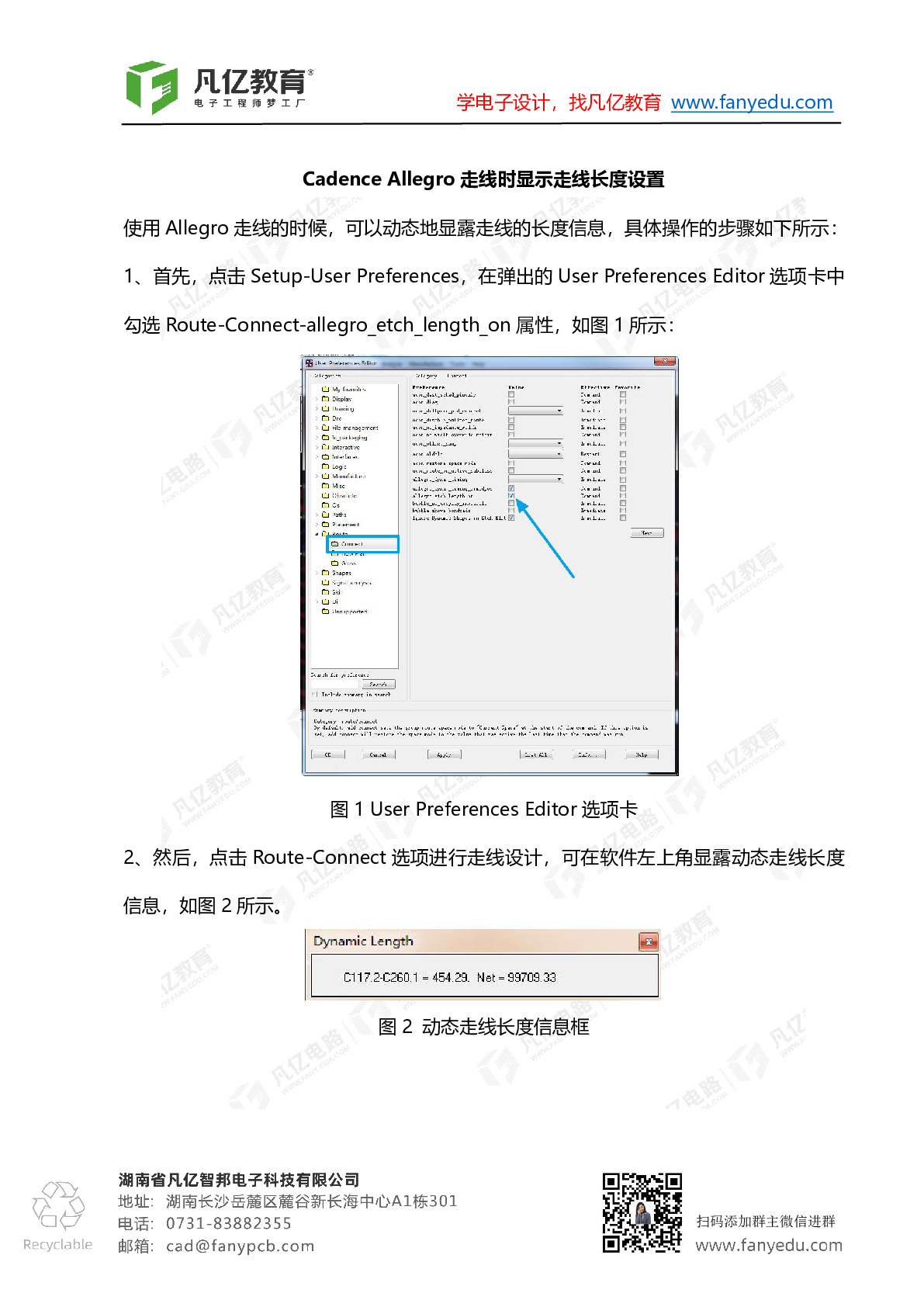

设计PCB过程中,若设计中有差分对信号,则需要将是差分的2个信号设置为差分对,设置差分对有2种方式:手动添加及自动添加一、手动添加差分对:1、点击Setup-Constraints-Constraint Manager调出CM规则管理器,然

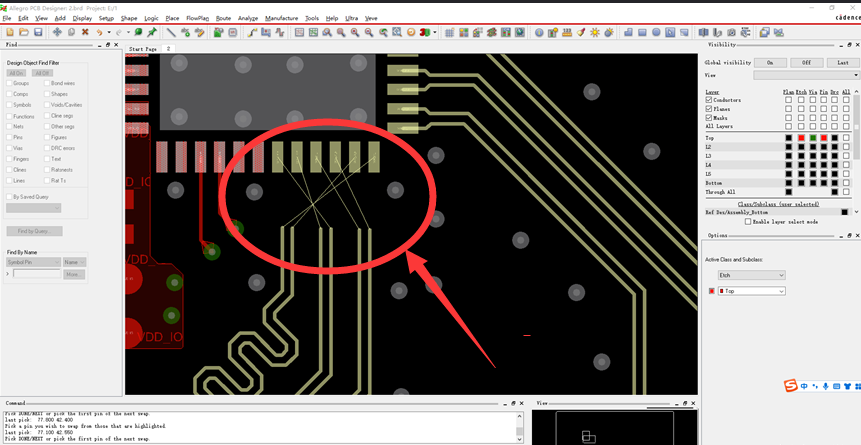

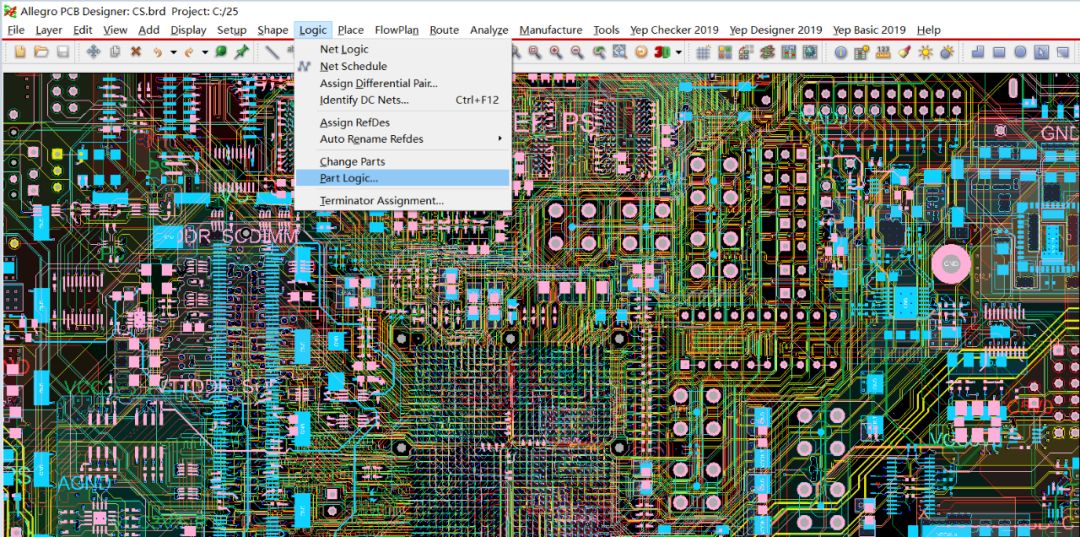

很多电子初学者在使用Cadence Allegro进行Layout设计时,会有一些mipi或lvds等差分走线,在走线时可能为了匹配线序,导致信号网络的走线是交叉,这样做不仅费时费力,还会影响信号质量,那么如何将这些器件的引脚交换过来?如图

一、课程详情这个是一个Cadence Allegro非常经典的 6 层一阶盲打孔设计,基于三星系列 S3C6410 ,全程讲解了通过Cadence Allegro,运用-阶盲埋孔的技术进行工控核心板卡的 PCB 设计教程视频,从前期的原理图导入,到后期输出生产文件( GERBER)的全过程。

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是Allegro)。

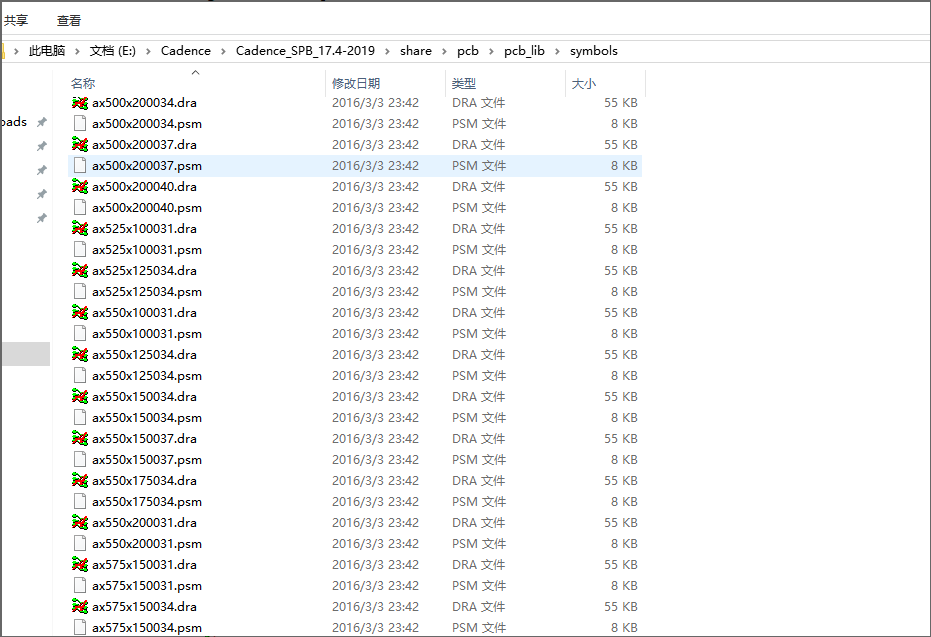

Cadence Allegro软件会自带的一些常用的PCB封装库,大家可以自行调用,它所存储的路径为:X:\Cadence\Cadence_SPB_17.4-2019\share\pcb\pcb_lib\symbols,如图所示:

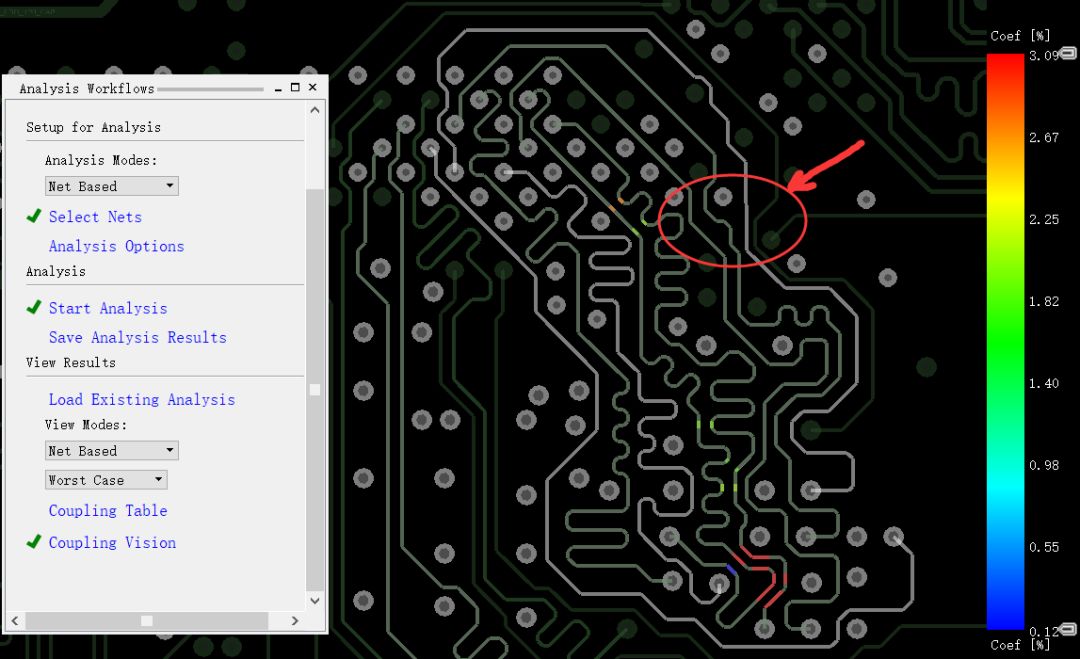

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。 PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。下面是在SigXplorer里面搭建了一个串扰的仿真链路,黄色部分就是得到的信号之间的串扰分析结果。

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一套完整的、高性能印制电路板设计套件。它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段进行定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产。Allegro是我们目前高速PCB设计中使用最多的工具。

扫码关注

扫码关注